# GE-235 AUXILIARY ARITHMETIC UNIT

REFERENCE MANUAL

GENERAL 👺 ELECTRI

# GE-235 AUXILIARY ARITHMETIC UNIT

JANUARY 1964

Revised June 1964

GENERAL E ELECTRIC

### PREFACE

This manual describes the functions and operations of the GE-235 Auxiliary Arithmetic Unit (AAU). It tells how the AAU operates and gives a detailed description of all instructions used in writing the program. Included in the Appendix of the manual is a list of available AAU routines which can be obtained from the Computer Department Program Library, P. O. Box 2961, Phoenix, Arizona 85002.

Detailed information for the GE-235 system is found in the following manuals:

GE-235 System Manual (CPB-267A)

GE-235 Central Processor Reference Manual (CPB-374).

This publication is a new edition and supersedes the GE-235 Auxiliary Arithmetic Unit Reference Manual (CPB-329), which should no longer be used. Send comments about this publication to Technical Writing, General Electric Computer Department, Drawer 270, Phoenix, Arizona 85001.

(c) 1964 by General Electric Company

# CONTENTS

|          |                                        | Page |

|----------|----------------------------------------|------|

| 1.       | GENERAL DESCRIPTION                    |      |

|          | Functions                              | 1    |

|          | Compatibility                          | 1    |

|          | Control                                | 2    |

|          | Priority                               | 2    |

|          | Modes                                  | 3    |

|          | Normalized Floating-Point Mode         | 3    |

|          | Unnormalized Floating-Point Mode       | 3    |

|          | Double Precision Fixed-Point Mode      | 4    |

|          | Trapping Mode                          | 4    |

|          | Registers                              | 4    |

|          | AX-Register                            | 4    |

|          | BX-Register                            | 6    |

|          | QX-Register                            | - 6  |

|          | IX-Register                            | 6    |

|          | SX-Register                            | 6    |

| 2.       | PROGRAMMING                            |      |

| ۷.       |                                        |      |

|          | Functions of the Central Processor     |      |

|          | General Instructions                   | 7    |

|          | Arithmetic and Load/Store Instructions | 7    |

|          | Test and Branch Instructions           |      |

|          | Trapping Mode                          |      |

|          | Word Formats                           | 8    |

|          | Instruction Words                      |      |

|          | Data Words                             |      |

|          | Exponential Arithmetic                 | 13   |

|          | Addition and Subtraction               | 13   |

|          | Multiplication                         | 13   |

|          | Division                               | 14   |

|          | Instructions                           | 14   |

|          | General Instructions                   | 15   |

|          | Arithmetic Instructions                |      |

|          | Test-and-Branch                        |      |

|          | Program Considerations                 |      |

|          | Setting the Calculation Mode           |      |

|          | Setting the Trapping Mode              | 39   |

| 3.       | OPERATING THE GE-235 AAU               |      |

|          | Operating Logic                        | 42   |

|          | AAU Controls and Indicators            |      |

|          | Central Processor AAU Indicators       | 47   |

|          | APPENDIXES                             |      |

| Α.       | AAU PROGRAM LIBRARY ROUTINES           | Δ_1  |

| н.<br>В. | LIST OF INSTRUCTIONS                   |      |

| D.<br>C. | AAU HALT CONDITIONS                    |      |

| - •      |                                        | · ·  |

## ILLUSTRATIONS

| Figure |                                                     | Page |

|--------|-----------------------------------------------------|------|

| 1.     | GE-235 AAU Subsystem                                | 2    |

| 2.     | Major Registers and Functional Logic Diagram        | 5    |

| 3.     | Fixed-Point Data Word Format                        | . 9  |

| 4.     | Format of a "Product" of a Fixed-Point Number       | 9    |

| 5.     | Floating-Point Data Word Format                     | 11   |

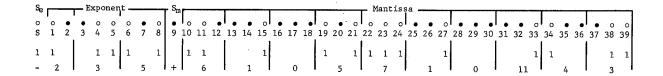

| 6.     | Floating-Point Number                               | 12   |

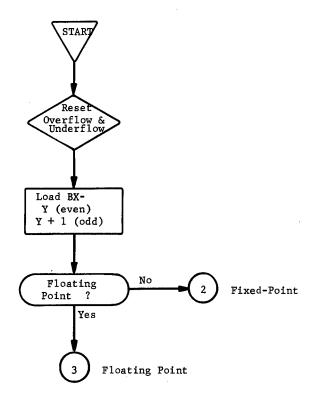

| 7.     | Initiation of Arithmetic Instruction                | 19   |

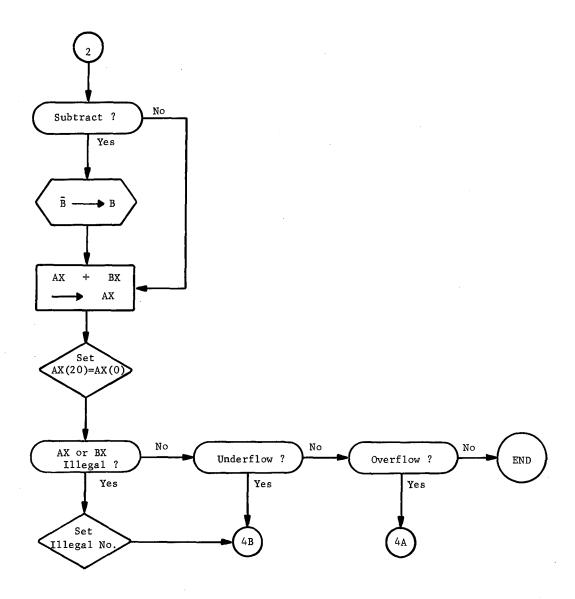

| 8.     | Fixed-Point FAD, FSU                                | 22   |

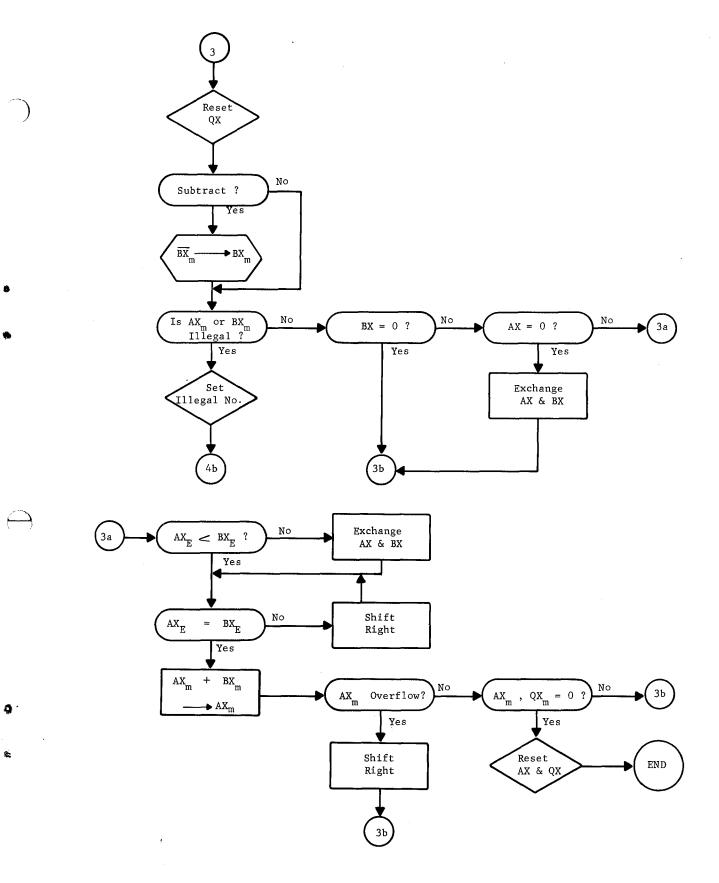

| 9.     | Floating-Point FAD, FSU                             | 23   |

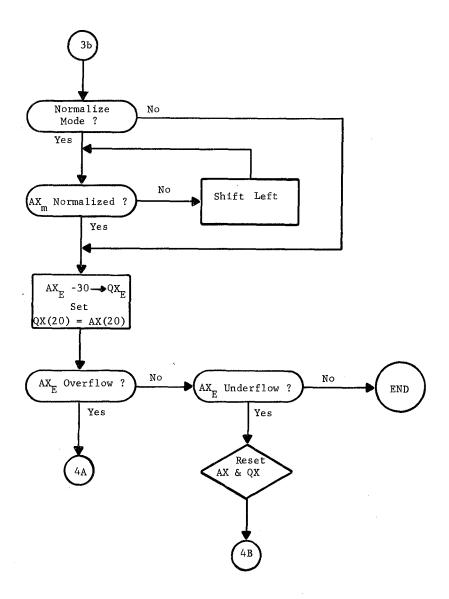

| 10.    | Normalization of Floating-Point Numbers             | 24   |

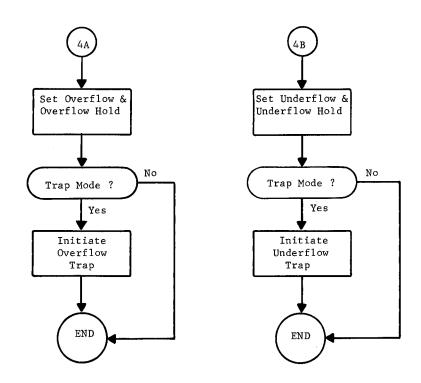

| 11.    | Setting Holds and Initiation of Trap Operation Mode | 25   |

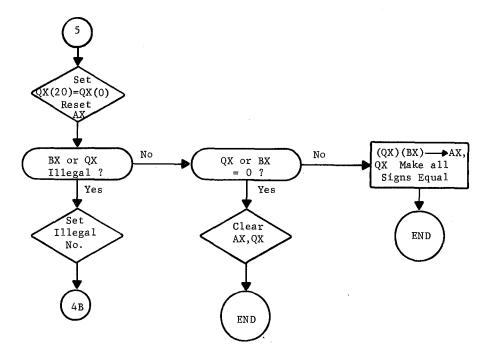

| 12.    | Fixed-Point FMP                                     | 28   |

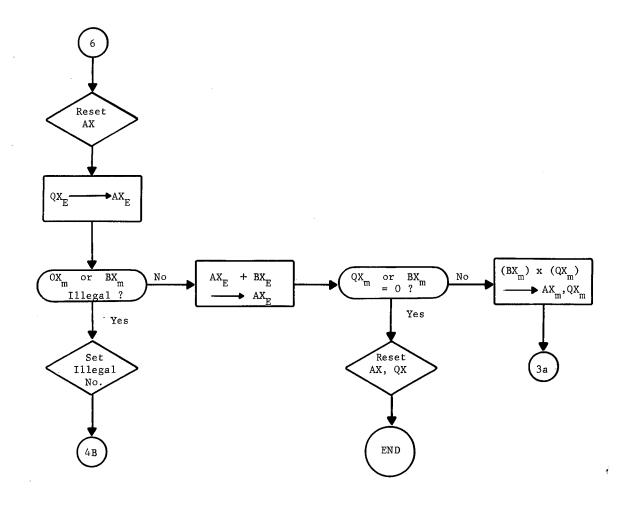

| 13.    | Floating-Point FMP                                  | 29   |

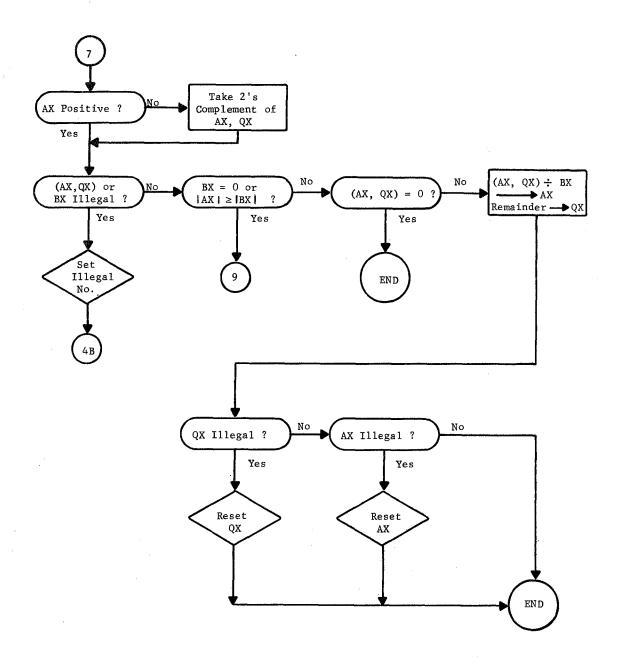

| 14.    | Fixed-Point FDV                                     | 32   |

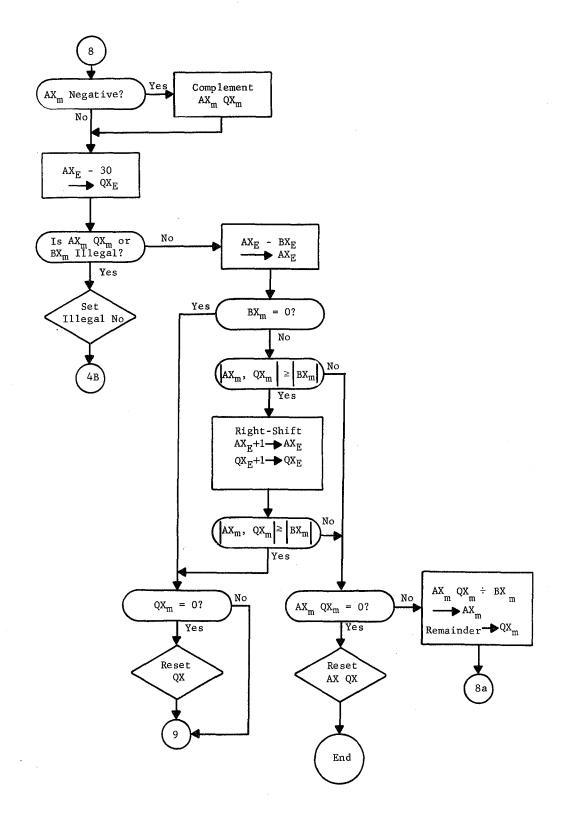

| 15.    | Floating-Point FDV                                  | 33   |

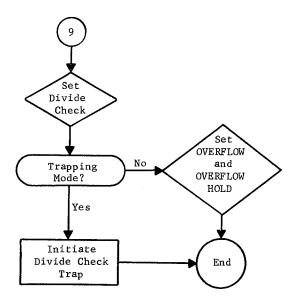

| 16.    | Setting Divide Check                                | 34   |

| 17.    | Normalization of Floating-Point FDV                 | 34   |

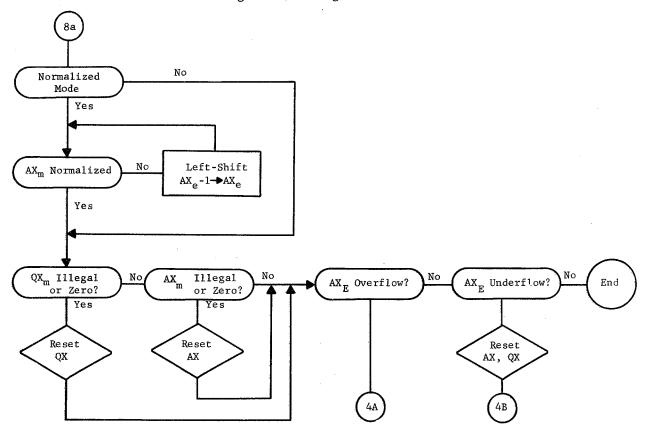

| 18.    | Setting Mode for Calculation                        | 38   |

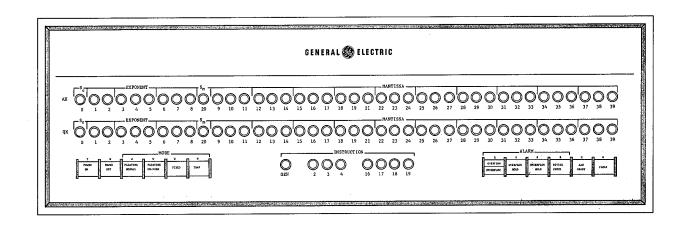

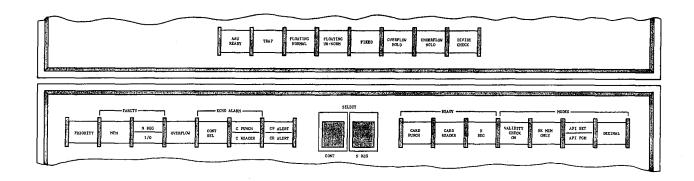

| 19.    | GE-235 AAU Control and Indicator Panel              | 43   |

| 20.    | Central Processor AAII Indicators                   | 47   |

GE-235 AUXILIARY ARITHMETIC UNIT

### 1. GENERAL DESCRIPTION

The Auxiliary Arithmetic Unit (AAU) is one of the many devices designed to further increase the capabilities of the GE-235 Information Processing System to handle mass detailed data. It is an extension of the central processor with large registers permitting calculations of great complexity and provides high-speed, double precision fixed-point and floating-point arithmetic capability.

The arithmetic capability of the AAU includes add, subtract, multiply, divide, normalized and unnormalized floating-point operands and double length (40-bit) fixed-point operands. The central processor of the GE-235 system continues standard arithmetic operations when the system includes an AAU.

### **FUNCTIONS**

The central processor of the GE-235 system performs the following major functions for the AAU:

- 1. Instruction retrieval

- 2. Address modification, if required

- 3. Partial instruction decoding

- 4. Operand retrieval and storage, when required

- 5. Control of transmission of instructions and data to the AAU

- 6. Synchronization of AAU operations with the central processor

- 7. Formulation of branch decisions based on AAU status indicators

- 8. Execution of a program interrupt based on AAU trap signals.

The AAU has its exclusive, high-speed data path to the central processor making it an extension of the arithmetic section and not a peripheral. Figure 1 illustrates in block diagram the GE-235 AAU subsystem.

### COMPATIBILITY

The basic user-oriented design philosophy of the GE-235 system is the same as that of the GE-205, GE-215, and GE-225, which have proved themselves fast, accurate, reliable, and

economical in widely divergent fields. As a result of their design similarity, all programs and applications originally designed for the other members of the Compatibles/200 systems can immediately be processed on a GE-235 having the same system configuration.

Figure 1. GE-235 AAU Subsystem

### CONTROL

All AAU instructions and information (operand words) originate with the central processor. The AAU receives its instructions simultaneously with the central processor. The instruction remains in the I-Register of the central processor until all indexing and accessing of memory for that instruction are complete.

### PRIORITY

The AAU is granted access to memory by the central processor priority control. The AAU decodes and executes its own instructions. All communication with the central processor memory is performed on a priority basis.

### MODES

The AAU performs calculations--at the option of the programmer--in one of the following three arithmetic modes:

- 1. Normalized floating-point

- 2. Unnormalized floating-point

- 3. Double precision fixed-point

A trapping mode is provided on the GE-235 AAU. This is an important feature which saves program running time by eliminating separate checking instructions following each possibility of overflow, underflow, divide check, or illegal numbers. The trapping mode can be set along with any one of the arithmetic modes under program control.

The central processor is readily adaptable to computing ranges of numbers with fixed points, such as whole numbers or whole numbers with fixed fractions. (For example: dollars and cents where the fractional portion of the number is always two decimal digits.) When the calculations involve numbers that have varying format or floating point, such as in scientific calculations, the central processor would have to keep track of the fractional point (radix point) by program. This is a lengthy and time-consuming operation; however, the GE-235 AAU simplifies programming and saves time since the floating point calculation or consideration is made by the hardware as normalized or unnormalized.

### Normalized Floating-Point Mode

A normalized number is one in which the most-significant nonzero digit of the fraction is next to the decimal point. For example, the decimal number 1234 would be:

$.1234 \times 10^4$ .

Both positive and negative numbers are adjusted so that the fractional value of the number is in a prescribed range when using the normalized floating point mode. Normalized floating-point numbers are described in detail under "Data Words" in Chapter 2.

### Unnormalized Floating-Point Mode

An unnormalized number is one in which zeros precede the most-significant nonzero digit fraction to the right of the decimal point. For example, the decimal number 001234 would be:

$.001234 \times 10^6$ .

In scientific calculations, the decimal point can be any place in a number. The manner in which two numbers are aligned makes a great deal of difference in the answer if the decimal point is not in alignment. It is possible for the program to be written so as to align each and every decimal point for each and every calculation, but this process is cumbersome. The GE-235 AAU simplifies programming of whole and fractional number calculations, saving time in the process.

### Double Precision Fixed-Point Mode

In the fixed-point mode, arithmetic operation in the AAU is the same as it is in the central processor with the exception that the AAU registers are double length. Fixed-point numbers can be in the forms shown below:

62478 (integer) .62478 (fraction) 62.478 (mixed number)

### Trapping Mode

This mode can be set or reset by the program with any one of the arithmetic modes. In the trapping mode, an AAU overflow, underflow, illegal number, or divide check will cause a special program interrupt in the central processor. The trapping mode, however, will not interfere with the operation of the Automatic Program Interrupt option in the GE-235 central processor.

### REGISTERS

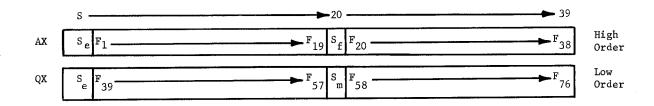

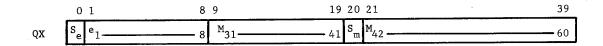

All AAU data words are first placed in the memory of the central processor as two 20-bit words, with bit meaning dependent upon the mode of operation selected. Executing a load operation will bring the two data words from memory through the central processor M-Register to be checked for parity. The AAU has a 40-bit buffer register which accepts the two 20-bit words to form one 40-bit AAU word, an Instruction Register to hold AAU instructions, a 40-bit Adder, and two other 40-bit registers, known as the AX- and QX-Registers. The size of these two registers permits both floating-point and fixed-point calculations on larger numbers than would normally be processed.

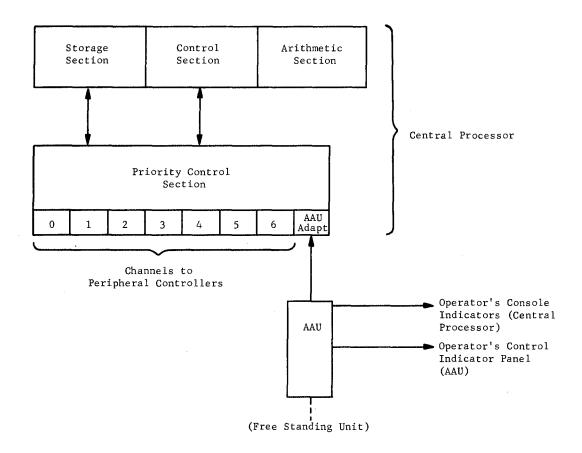

The AX-, BX-, QX-, and IX-Registers and the adder (SX) perform functions similar to their counterpart registers (A, B, Q, and I) in the GE-235 central processor. Figure 2 is a block diagram showing the data and control timing paths for the functional logic and the major registers of the GE-235 AAU.

### **AX-Register**

The AX-Register is a 40-bit accumulator which performs the following functions:

- Holds the addend prior to addition and the most-significant bits of the sum after addition

- Holds the minuend prior to the subtraction and the most-significant bits of the difference after subtraction

- Holds the most-significant bits of the product after multiplication

- Holds the most-significant bits of dividend prior to division and the entire quotient after division

- Receives the 40-bit operand (two GE-235 computer words) from the central processor M-Register via the BX-Register during a load operation, and provides the 40-bit operand to be stored in memory via the BX- and M-Registers during a store operation.

Figure 2. Major Registers And Functional Logic Diagram

### BX-Register

The BX-Register is a 40-bit buffer register and distributor which performs the following functions:

- Holds the addend prior to addition

- Holds the subtrahend prior to subtraction

- Holds the multiplicand prior to multiplication

- Holds the divisor prior to division

- During a load operation, it receives two 20-bit words sequentially from the M-Register, assembles them into one 40-bit operand, and transmits the operand to the AX-Register.

During a Store operation, it disassembles the 40-bit operand received from the AX-Register and transmits two 20-bit words, most significant half first, to the M-Register

- Performs all complementation that is required by the AAU.

### QX-Register

The QX-Register is a 40-bit accumulator which performs the following functions:

- Conditionally holds the least-significant bits of the sum after addition

- Conditionally holds the least-significant bits of the difference after subtraction

- Holds the least-significant bits of the product after multiplication and the entire multiplier before multiplication

- Holds the least-significant bits of the dividend prior to division and the remainder after division.

### IX-Register

The IX-Register is a 7-bit instruction register. It contains the current AAU command being executed. The IX-Register receives bits 2, 3, 4, 16, 17, 18, and 19 from the central processor I-Register.

### SX-Register

The SX-Register, or adder, performs the following functions:

- Forty bit full binary adder during fixed point operations

- Thirty-one bit full adder for the mantissa during floating point operations

- Nine bit full adder for the exponent during floating point operations

- Adds the carry to the one's complement on all negate operations.

### 2. PROGRAMMING

The Auxiliary Arithmetic Unit is an on-line device and not a peripheral of the GE-235 system. It has its own channel (see Figure 1) for access to the central processor and has no separate controller.

### FUNCTIONS OF THE CENTRAL PROCESSOR

The central processor performs the function of instruction retrieval. An immediate decision is reached if the retrieved instruction is for the AAU. Once the AAU is given an instruction to perform, it then operates independently of the central processor. The central processor is restrained from receiving priority until the AAU instruction is completed.

### General Instructions

All general instructions are examined for zero content of bits 5-15. If all bits are zero, the instruction is immediately transferred to the AAU and executed.

### Arithmetic and Load/Store Instructions

Either of these types of instruction may be address modified by the central processor. After possible indexing, the instruction is executed by the AAU using the central processor I-Register as the memory operand address register.

### Test and Branch Instructions

If the instruction is a BAR (test and branch for the AAU), the central processor interrogates the various status indicators of the AAU. The AAU replies to the query and the central processor performs the appropriate branching decision.

### TRAPPING MODE

The trapping mode is a standard feature of the GE-235 AAU, operating in a manner similar to the Automatic Program Interrupt (API) of the central processor. The trapping mode is not a normal mode of operation of the AAU. Unless this mode is set by program, the main program will not be interrupted in the event of overflow, underflow, divide check, or illegal number errors. A discussion of the use of the trapping mode will be found under "Programming Considerations," page 39.

### WORD FORMATS

The formats for instruction and data words for the GE-235 AAU are compatible with the GE-215/225 AAU.

### Instruction Words

Instruction words are contained in a single address word consisting of 20 bits. The basic formats for the 3 types of instruction words are as follows:

### GENERAL INSTRUCTION WORDS

| 0 4               | 4 5 |                 | 15 | 16                | 19  |

|-------------------|-----|-----------------|----|-------------------|-----|

| Operation<br>Code |     | Operand Address |    | Suffix<br>Opr. Co | ode |

### TEST-AND-BRANCH INSTRUCTION WORDS

| 0                   | 4 | 5 | 6 | 7 | 15 | 16               | 19   |

|---------------------|---|---|---|---|----|------------------|------|

| Operation<br>• Code |   | Х | X |   |    | Suffix<br>Opr. 0 | code |

### ARITHMETIC INSTRUCTION WORDS

| 0                 | 4 | 5 | 6 | 7 | . 19            |   |

|-------------------|---|---|---|---|-----------------|---|

| Operation<br>Code |   | X | х |   | Operand Address | l |

### Data Words

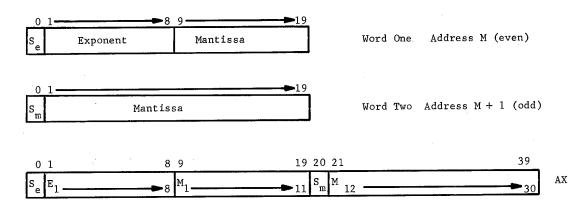

Data for all AAU operations can exist in memory in any of three different modes--fixed-point, normalized floating-point, and unnormalized floating-point. All AAU data words exist in the central processor memory as two 20-bit words with the bits of each word having meaning according to the mode selected. Thus, when an instruction to load the AAU with the contents of memory location 3200 (FLD 3200) is received and executed by the AAU, the contents of 3200 and 3201 are brought into the AAU. The format in which the contents of 3200 and 3201 are interpreted depends upon the mode in which the AAU is operating.

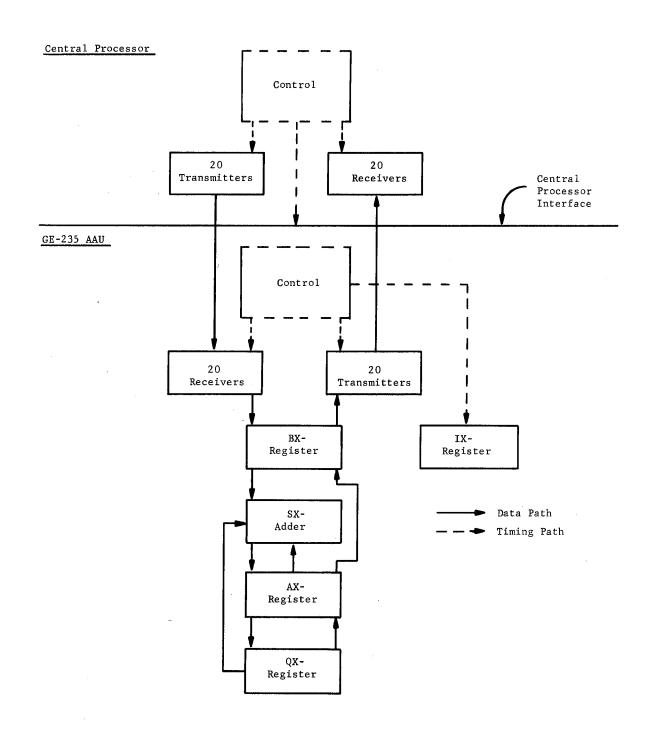

FIXED-POINT WORDS in memory are in the format as shown in Figure 3. To illustrate, the FLD 3200 instruction is used. Note that the signs of word one and word two are identical for fixed-point words. Thus, when two data words from memory enter the AAU, they appear in the AX-Register as one 40-bit word. As shown, the fixed-point word in the AX-Register consists of 38 information bits, plus two identical sign bits. Similarly, a fixed-point word in the QX-Register also consists of 38 information bits and 2 sign bits.

Fixed Point Data Word Format

Figure 3. Fixed-Point Data Word Format

Bit one-- $S_e$ --is the sign bit of the entire word (38 bits), bit 20-- $S_m$ --has no significance in fixed-point words. Any arithmetic operation will cause bit position  $S_m$  to agree with bit position  $S_e$ .

If The Fixed-Point Number is the product of a multiply operation, it is stored in the AX- and QX-Registers in the format shown in Figure 4.

NOTE:  $F_{76}$  now has the value  $2^0$  and  $F_1$  has the value  $2^{75}$ . All signs set to agree.

Figure 4. Format of a "Product" of a Fixed-Point Number

An example of fixed-point numbers follows:

|                  | : | AX-Regis | ter 1 | Bit Position | $\underline{\mathbf{Remarks}}$ |  |  |  |

|------------------|---|----------|-------|--------------|--------------------------------|--|--|--|

| Value            | S | 1 - 19   | 20    | 21 - 39      |                                |  |  |  |

| Largest Positive | 0 | 11       | 0     | 11           |                                |  |  |  |

| +1               | 0 | 00       | 0     | 01           |                                |  |  |  |

| Zero             | 0 | 00       | 0     | 00           |                                |  |  |  |

| -1               | 1 | 11       | 1     | 11           | Two's complement notation for  |  |  |  |

| Largest Negative | 1 | 00       | 1     | 0, 1         | negative numbers.              |  |  |  |

An Illegal Fixed-Point Number is not generated by the AAU, except as the result of overflow or underflow. If an arithmetic operation is attempted, the operation may or may not be performed; however, the underflow and illegal numbers are set.

Example: Illegal fixed-point numbers

| AX-Register |   |     | 19      |   |    |         |

|-------------|---|-----|---------|---|----|---------|

| _           | 1 | 0   | <br>. 0 | 0 | 0. | <br>. 0 |

|             | 1 | 0 , | <br>. 0 | 1 | 0. | <br>. 0 |

FLOATING-POINT WORDS consist of two parts, an exponent and a mantissa. The 4 basic terms used in floating-point arithmetic operations are as follows:

- 1. Exponent. As used with the AAU, the exponent (or characteristic) is the 9 most-significant bits (8 numeric bits and a sign bit) of a double word (see Figure 5). These bits designate to what power of two the mantissa portion of the word must be raised.

- 2. Mantissa. In the AAU, the mantissa is the 30 least-significant bits of a double word. The radix point (see Radix Point described below) for these 30 bits is assumed to be to the left of the most significant of the 30 bits. Thus, the mantissa is fractional in value (see Figure 5).

The mantissa is multiplied by two raised to the exponential power expressed in bits 0-8 to give the entire word the desired numeric value.

- Radix Point. The point in any numbering system which separates the whole integers from the fraction. Thus, the decimal point is a radix point for the decimal system; a binary point is the radix point for the binary system. Because the computer and AAU operate in binary rather than in decimal digits, the term "decimal point" should be replaced by the term "binary point."

- 4. Normalization. In the AAU, positive and negative numbers are normalized, or adjusted, so that the mantissa lies in the prescribed range; the absolute value of the mantissa must be greater than (or equal to) 1/2 and less than 1. Algebraically, this is expressed as:

$1/2 \leq (\text{mantissa}) < 1$

Positive Numbers Are Normalized by shifting the mantissa left until its most-significant bit (bit 9 in the AX-Register) is a 1-bit. For each position shifted left, one is subtracted from the exponent.

Negative Numbers Are Normalized by shifting the mantissa left until its most-significant bit (bit 9 in the AX-Register) is a 0-bit or there is a 1-bit followed by zeros in all other mantissa bits. For each position shifted left, one is subtracted from the exponent.

The AAU generates normalized results of addition, subtraction, multiplication, and division in the AX-Register if it has been set into the normalized floating point mode by the programmer. The numbers to be operated on do not have to be in normalized form prior to the operation.

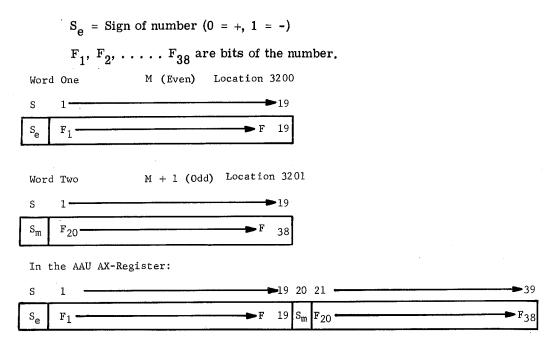

Floating-point numbers are stored in memory and in the AX-Register in the following forms and formats, as shown in Figure 5. The binary point is assumed to be before the first bit (bit 9) of the mantissa. This format produces a binary number with a 30-bit mantissa and a binary characteristic range of -256 to +255. This is approximately equal to a decimal number with

a 9-digit mantissa and a decimal range of  $10^{-77}$  to  $10^{+77}$ . The fact that two words are used allows one of the sign positions to be applied to the exponent.

$S_e$  = Sign of the exponent part  $S_m$  = Sign of the mantissa (fraction) part  $E_1 \dots E_8$  = Bits of the exponent  $M_9 \dots M_{39}$  = Bits of the mantissa (fraction)

Figure 5. Floating-Point Data Word Format

If the Floating-Point Number is the result of multiplication, addition, or subtraction, the minor half (low order) appears in the QX-Register in the format shown in Figure 6. The major half (high order) will appear in the AX-Register.

Figure 6. Floating-Point Number

The value of the QX exponent--e--is set equal to the value of the AX exponent--E--minus thirty (e=E-30). The sign of the QX fraction--S  $_{\rm m}$ --is set to agree with the sign of the AX fraction--S  $_{\rm m}$ -

The AAU operates in the fractional floating-point mode; that is, a fractional mantissa and an integral exponent. The use of any AAU instructions for floating point operations assumes that the memory operands are in the floating-point format.

An example of floating-point numbers follows:

### AX-Register Bit Positions

|                   | S  | 1 8  | 9 19 | 20   | 21 39   |

|-------------------|----|------|------|------|---------|

| Largest Positive  | 0  | 1111 | 111. | .0.  | . 11 11 |

| +1                | 0  | 0001 | 100. | .0.  | . 00 00 |

| Smallest Positive | 1_ | 0001 | 000. | .0.  | . 00 01 |

| 0                 | 0  | 0000 | 000. | . 0. | . 00 00 |

| Smallest Negative | 1  | 0001 | 111. | .1.  | .1111   |

| -1                | 0  | 0001 | 100. | .1.  | . 00 00 |

| Largest Negative  | 0  | 1111 | 000. | .1.  | . 00 01 |

The "largest negative" number is the number farthest from zero with negative sign. The "smallest negative" is the number nearest to zero with negative sign.

An Illegal Floating-Point Number is one having a mantissa which is one past the range of the AAU in either the negative or positive direction. If any arithmetic operation is attempted, the complete operation will not be performed, the underflow and illegal number will be set. Illegal floating-point numbers are shown in the following examples:

### Example 1.

### AX-Register Bit Positions

| Illegal floating | S | 1 - | 8 | 9 | 19 | 20 | 21 - 39 |

|------------------|---|-----|---|---|----|----|---------|

| point number (s) | 1 |     |   |   |    |    | . 00    |

| •                | 0 | any | 7 | 0 | 0. | 1. | . 00    |

This number has a mantissa which is one past the range of the AAU in the negative direction.

Example 2. The following number is treated as zero for any multiply or divide operation (not add or subtract). Any multiply or divide operation attempted will cause the exponent to be reset to zero. The operation will then proceed as though the number were zero.

Example 3. The following number has an exponent which is one past the range of the AAU in either the positive or negative direction. It may be loaded and stored and operated on arithmetically. The exponent will be treated as -256<sub>10</sub>.

SUBROUTINES are required initially to create floating-point words from BCD data or to create BCD words from floating-point format. This conversion from one to another is possible using conversion routines CD225C2.006/8 obtained from the GE Program Library or through the local sales office of the General Electric Computer Department.

### EXPONENTIAL ARITHMETIC

To perform arithmetic operations in the floating-point format, several requirements must be met. For addition and subtraction problems, the exponents of the numbers involved must be equal. It is not probable that a common exponent will be used in all problems; however, the AAU automatically adjusts exponents. The AAU adjusts the exponent with the smaller numeric value. Adjustment is accomplished by automatically shifting the mantissa of the word with the smaller exponent right and incrementing its exponent by the number of positions shifted.

### Addition and Subtraction

Once exponents are equalized, addition or subtraction of the mantissas can occur. The exponent of the answer is the adjusted exponent while the mantissa of the answer is the sum or difference of the shifted mantissas.

### Multiplication

For multiplication, exponents are added and mantissas are multiplied. The resultant exponent in multiplication is the algebraic sum of the original exponents, while the resultant mantissa is the product of multiplying the original mantissas.

### **Division**

In division, the exponent of the divisor is subtracted from the exponent of the dividend, and the mantissa of the dividend is divided by the mantissa of the divisor. The resultant exponent is the algebraic difference between the dividend and the divisor exponents. The resultant mantissa is the result of the algebraic division of the dividend mantissa by the divisor mantissa. In summary, floating-point division causes the subtraction of exponents and division of mantissas.

OVERFLOW AND UNDERFLOW in floating-point arithmetic operations, can result during both the normalized and unnormalized arithmetic modes.

Overflow occurs if the exponent of a final result in the AX-Register exceeds  $+377_8$  ( $+225_{10}$ ).

Underflow occurs when the exponent of a final result in the AX-Register becomes less than  $-400_8$  (-256<sub>10</sub>).

### OVERFLOW OR UNDERFLOW can result at any of these times:

- During the formation of the initial estimate of the result exponent

- During a right shift one and add one as a result of mantissa overflow

- During the normalization of a result (normalized mode). Normalization involves shifting the mantissa left N places and subtracting N from the exponent, possibly causing underflow, N being the number of leading zeros in a positive mantissa or leading ones in a negative mantissa.

No single AAU instruction will ever result in setting both overflow and underflow.

Whenever underflow occurs, the AX-Register is cleared to zero if the AAU is in either the normalized or unnormalized floating-point modes. This assures that zero is always a valid replacement for the true result when underflow occurs. The clearing of AX does not cause reset of the underflow.

### **INSTRUCTIONS**

Instructions for the GE-235 AAU are divided into 3 categories, as follows:

- 1. General Instructions:

- a. Control (sets mode of operation)

- b. Data Transfer (load/store) within the AAU

- c. Reset (underflow/overflow)

- d. Normalization

- 2. Arithmetic Instructions:

- a. Arithmetic operations: add, subtract, multiply, and divide

- b. Data Transfer (load/store) between the AAU and central processor

- 3. Test-and-Branch Instructions.

The description of instructions in this manual use the following format, explained in the key below.

| MAQ |   | A | 3100002 |

|-----|---|---|---------|

| 2   | 3 | 4 | 5       |

- 1. Name of instruction (operation to be performed).

- 2. General Assembly Program mnemonic operation code.

- 3. General Assembly Program Operand field symbol:

- a. M indicates that the operand field in this instruction is occupied by the address of a memory location (address may be either actual or symbolic).

- b. A three-character mnemonic code indicates the specific condition (true or false) of a test and branch instruction.

- 4. General Assembly Program symbol X field:

- a. X indicates that the address in the operand field of the instruction may be automatically modified by using address modification words. Omission of this symbol indicates the instruction cannot be modified in this way.

- b. A indicates that the AAU registers are affected by the instruction in a similar manner to the registers of the central processor.

- 5. Representation of the machine coding of the instruction in octal notation.

### General Instructions

General Instructions do not require memory reference. The operation codes are defined by bits S-4 and 16-19 of the instruction word, with all other bits zero. The general instructions are further defined by type of instruction, as follows:

- 1. Control

- 2. Data Transfer (within the AAU)

- 3. Reset

- 4. Normalize

CONTROL INSTRUCTIONS set the mode of operation to be performed upon the data words received. The GE-235 AAU is set to normalized floating-point mode under the 3 following conditions:

- 1. Power-on time

- 2. When the CLEAR switch is depressed on the AAU

- 3. When the RESET MODES switch is depressed on the central processor console.

It is necessary to set the mode of operation by a SET MODE instruction before giving an arithmetic instruction to obtain positive control over the AAU. Once a SET MODE instruction is executed, the AAU executes all arithmetic instructions in that mode until the mode is changed by another SET MODE instruction.

### SET FIXED-POINT MODE

SET FIXPOINT

3500010

The AAU is set to execute AAU arithmetic instructions in double precision fixed-point mode.

### SET NORMALIZED FLOATING-POINT MODE

SET NFLPOINT

3100010

The AAU is set to execute AAU arithmetic instructions in normalized floating-point mode.

### SET UNNORMALIZED FLOATING-POINT MODE

SET UFLPOINT

3200010

The AAU is set to execute AAU arithmetic instructions in unnormalized floating-point mode.

### SET TRAPPING MODE

SET TRPMODE

3100001

The AAU is set to interrupt the central processor upon detection of subsequent overflow, underflow, or divide check conditions. An illegal number causes an underflow condition in the trapping mode.

The overflow hold, underflow hold, divide check, and illegal number statuses are not reset by this instruction.

The AAU remains in the trapping mode until execution of a SET NTPMODE instruction or until the RESET MODES switch on the central processor console is depressed.

### SET TRAPPING MODE OFF

SET NTPMODE

3200001

The AAU trapping mode is turned off.

The overflow hold, underflow hold, divide check, and illegal number statuses are not affected by this instruction.

<u>DATA TRANSFER INSTRUCTIONS</u> are similar to certain central processor data transfer instructions. They involve transfer of data between arithmetic registers within the AAU and are specified by mnemonic codes similar to those for the central processor. AAU data transfer instructions are identified by placing the letter A in the X column (card column 20) of the General Assembly Program coding sheet.

### CLEAR AX-REGISTER

CAX

Α

3200005

The AX-Register of the AAU is cleared to all zeros.

### CLEAR OX-REGISTER

CQX

Α

3500005

The QX-Register of the AAU is cleared to all zeros.

### LOAD AX FROM QX

LAQ

Α

3600002

The contents of the QX-Register replace the contents of the AX-Register. The contents of the QX-Register are unchanged.

### LOAD QX FROM AX

LOA

Α

3200002

The contents of the AX-Register replace the contents of the QX-Register. The contents of the AX-Register are unchanged.

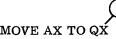

### MOVE AX TO QX

MAQ

$\mathbf{A}$

3100002

The contents of the AX-Register replace the contents of the QX-Register. The contents of the AX-Register are reset to zeros.

### EXCHANGE AX AND QX

XAQ

A

3500002

The contents of the AX- and QX-Registers are interchanged.

RESET INSTRUCTIONS are used to reset the OVERFLOW HOLD, UNDERFLOW HOLD, and DIVIDE CHECK indicators.

### RESET INDICATORS

RIN

3500004

The OVERFLOW HOLD, UNDERFLOW HOLD, and DIVIDE CHECK indicators are turned off. The internal illegal number indicator is also turned off.

### RESET OVERFLOW HOLD

ROV

3100004

The OVERFLOW HOLD indicator is turned off.

### RESET UNDERFLOW HOLD

RUN

3200004

The UNDERFLOW HOLD indicator is turned off.

The OVERFLOW HOLD, UNDERFLOW HOLD, and DIVIDE CHECK indicators will have been set as a result of overflow, underflow, divide check and illegal number conditions.

NORMALIZE INSTRUCTION. This instruction operates correctly only on floating-point data. The instruction itself is not mode dependent, and operates correctly in all three arithmetic modes.

### NORMALIZE AX AND QX

NOX

3100005

The floating-point operand in the AX- and QX-Registers is normalized by shifting the mantissa left until a 1-bit is detected in the most-significant bit position, AX (9) for positive numbers, or a 0-bit is detected in AX (9) for negative numbers. For each bit position shifted, one is subtracted from the exponent in AX. Bits from QX (9) shift into position AX (39). After normalization, the exponent in the QX is set to 30 less than the exponent of AX. The sign of QX is set to the original sign of the AX.

Zero is defined as a normalized number.

### Arithmetic Instructions

Arithmetic instructions (add, subtract, multiply, and divide) include data transfer (load/store) operations on data words according to the mode (fixed, normalized, or unnormalized) as specified by a control SET MODE instruction. Figure 7 is an illustration of the initiation of an instruction.

Figure 7. Initiation of Arithmetic Instruction

Bits S-4 of the instruction word defines the operation to be performed. Bits 5-6, if set, specify index word modification. Bits 7-19 specify the operand (memory) address of the data word.

If index word modification is specified, the central processor performs the required index modification. The instruction is then executed by the AAU using the central processor I-Register as the memory operand address register.

If index word modification is not specified, the operand address must be an even numbered location in memory and be greater than 15 for proper execution. If the address is odd, either the contents of the odd location will be loaded into both halves of the BX-Register, or the contents of BX will be stored so that first the most-significant half of BX (S-19) appears in the odd location and then BX (20-39) is written over BX (S-19) in the same odd location.

Floating point operations assume that the operands of the data word are already in floating-point format. If the operand is not in floating-point format, it can be converted by means of a subroutine furnished for this purpose (CD225C1.006/8).

ARITHMETIC OPERATIONS are performed by the AAU upon operands whose memory address is greater than 15, unless the instruction is index modified. Instructions for arithmetic operations are: FAD, FSU, FMP, and FDV.

Each instruction is described for each of the 3 operating modes: fixed, normalized, and unnormalized.

ADD

FAD M X

31MMMMM

The contents of memory location M and M+1 are added algebraically to the contents of the AX-Register. The contents of M and M+1 are unchanged.

### Fixed-Point Mode

- The sum of the contents of M and M+1 plus the contents of AX is left in AX-Register with bits 0 and 20 (sign bits) set to agree

- QX Register is unchanged

- Overflow is set if the capacity of the AX-Register is exceeded in a positive direction during the add operation. The AX-Register remains in an overflow condition.

- Underflow is set:

- 1. If the capacity of the AX-Register is exceeded in a negative direction during an add operation. The AX-Register remains in an underflow condition.

- 2. If an illegal number is detected at the start of the operation in either the AX- or BX-Registers. An illegal number causes both underflow and illegal number conditions to be set.

### Normalized Floating Point Mode

- The floating-point number in M and M+1 are loaded into the BX-Register

- QX Register is cleared

- A check is made to determine if either the AX- or BX-Register contain an illegal number in the mantissa. If either or both do, the arithmetic operation is terminated with an UNDERFLOW (and illegal number) indication in the AAU

- The AX- and BX-Registers are examined for zero content and if either are found to contain zeros, the nonzero number is placed in the AX-Register and the contents are normalized. If neither AX nor BX are zero, then the exponents are compared

- If the exponent of the number in BX is algebraically smaller than the exponent in AX, BX and AX are interchanged—the smaller exponent is placed in AX

- Exponents are aligned by right shifting the AX-Register, adding one to the exponent for each position shifted, until the exponents are equal. Bits shifted out of AX-39 are shifted into QX-9; bits shifted out of QX-39 are lost

- When the exponents are aligned, the mantissas are algebraically added and mantissa overflow, if it occurred, is corrected. The sum of the mantissas in AX and QX is normalized

- Mantissa overflow is corrected by shifting the mantissa one bit position to the right and adding one to the exponent

- AX and QX mantissas are examined for zero content and, if found to contain zeros, the exponents are cleared and the operation is terminated. The AX- and QX-Registers are cleared

- If AX and QX mantissas are not zeros, the sum in the AX- and QX-Registers is normalized. Leading zeros (for positive mantissas) or ones (for negative mantissas) are stripped by left-shifting AX and QX and subtracting from the exponent. Bits from QX-9 are reintroduced into AX-39; AX and QX are left-shifted together. Zeros are introduced into QX-39.

- ullet Exponent of QX is set to AX<sub>E</sub>-30 so that the minor half of the sum will be properly scaled. If QX<sub>E</sub> underflows, no error is set.

- The QX mantissa sign (bit 20) is set to the same value as the AX mantissa sign

- A check is made to determine if overflow or underflow occurred

- Overflow is set if the exponent sum in the AX-Register exceeds +255<sub>10</sub>. AX- and QX-Register remain in an overflow condition

- Underflow is set:

- 1. If an illegal number is detected in the mantissa at the start of the operation in either the AX or BX Registers

- 2. If the exponent sum in AX is less than -256 $_{10}$ . The AX- and QX-Registers are cleared.

Unnormalized Floating-Point Mode. Same conditions prevail as set forth for normalized floating point mode, except the sum of mantissas in the AX- and QX-Registers is left in unnormalized form.

An execution of a fixed point add operation is shown in Figure 8.

Figures 9 and 10 illustrate the execution of a floating-point add operation.

Figure 11 shows how holds are set and the initiation of the trap operation takes place.

Figure 8. Fixed-Point FAD, FSU

Figure 9. Floating-Point FAD, FSU

Figure 10. Normalization, Floating-Point Numbers

Figure 11. Setting Holds and Initiation of Trap Operation Mode

### SUBTRACT

| FSU | M | X | 32MMMMM |

|-----|---|---|---------|

|     |   |   |         |

The contents of memory location M and M+1 are algebraically subtracted from the contents of the AX-Register. The contents of M and M+1 are unchanged.

### Fixed-Point Mode

- The contents of M and M+1 are loaded into the BX-Register. BX is complemented and added algebraically to the contents of the AX-Register. The difference is left in the AX-Register with bits 0 and 20 (sign bits) set to agree

- The QX-Register is unchanged

- Overflow is set if the capacity of the AX-Register is exceeded in a positive direction during a subtract operation. The AX-Register remains in an overflow condition

- Underflow is set:

- 1. If the capacity of the AX-Register is exceeded in a negative direction during a subtract operation. The AX-Register remains in an underflow condition.

- 2. If an illegal number is detected at the start of the operation in either the AX-or BX-Registers.

### Normalized Floating-Point Mode

- The floating-point number in M and M+1 is loaded into the BX-Register. The BX mantissa is complemented

- The QX-Register is cleared

- A check is made to determine if either the AX- or BX-Register contains an illegal number in the mantissa. If either or both do, the arithmetic operation is terminated with an UNDERFLOW (and illegal number) indication in the AAU

- If both registers contain legal numbers, they are examined for zero content and if either one is found to contain zeros, the nonzero number is placed in the AX-Register and the contents are normalized. If neither register contains zeros, then the exponents are compared

- If the exponent of the number in BX is algebraically smaller than the exponent in AX, BX and AX are interchanged—the smaller exponent is placed in AX

- Exponents are aligned by right-shifting the AX-Register, adding one to the exponent for each position shifted, until the exponents are equal. Bits shifted out of AX-39 are shifted into QX-9; bits shifted out of QX-39 are lost

- When exponents are aligned, the mantissas are algebraically added and mantissa over-flow, if it occurred, is corrected. The sum of the mantissas in AX and QX is normalized.

- Mantissa overflow is corrected by right-shifting the mantissa one bit position and adding one to the exponent.

- AX and QX mantissas are examined for zero content and if found to contain zeros the exponents are cleared and the operation is terminated. The AX- and QX-Registers are cleared

- If AX and QX mantissas are not zeros, the difference in the AX- and QX-Registers is normalized. Leading zeros (for positive mantissas) and ones (for negative mantissas) are stripped by left-shifting AX-QX and subtracting from the exponent; bits from QX-9 are reintroduced into AX-39; AX and QX are left-shifted together. Zeros are introduced into QX-39

- ullet Exponent of QX is set to AX<sub>E</sub>-30 so that the minor half of the difference will be properly scaled. If QX<sub>E</sub> underflows, no error is set

- The QX mantissa sign bit (20) is set to the same value as the AX mantissa sign

- A check is made to determine if overflow or underflow occurred

- Overflow is set if the exponent result in AX-Register exceeds +255<sub>10</sub>. AX- and QX-Registers remain in an overflow condition

- Underflow is set:

- 1. If an illegal number is detected in the mantissa at the start of the operation in either the AX or BX-Registers.

- 2. If the exponent result in AX is less than -256<sub>10</sub>. The AX- and QX-Registers are cleared.

Unnormalized Floating-Point Mode. Same conditions prevail as set forth for normalized floating-point mode, except: difference of mantissas in the AX- and QX-Registers is left in unnormalized form.

Figure 8 illustrates the execution of the FSU instruction during a fixed-point mode of operation.

Figures 9 and 10 illustrate the execution of the FSU instruction during the floating-point mode of operation.

### MULTIPLY

### FMP M X

### 35MMMMM

The contents of memory location M and M+1 are multiplied algebraically by the contents of the QX-Register. The contents of M and M+1 are unchanged.

### Fixed-Point Mode

- M and M+1 are loaded into the BX-Register. The AX-Register is cleared. Bit 20 of the QX-Register is set equal to QX-0

- A check is made to see if either BX- or QX-Registers contain an illegal number. If neither or both do, the arithmetic operation is terminated with an UNDERFLOW (and illegal number) indicators in the AAU

- If both Registers contain legal numbers, they are examined for zero content and if either or both contain zeros, the AX- and QX-Registers are cleared and the arithmetic operation is terminated

- If the BX- and QX-Registers contain legal nonzero numbers they are multiplied and their product is stored in the AX- and QX-Registers. The product is a 76-bit fixed-point number, right adjusted in AX and QX with four identical sign bits

- Overflow is not possible with legal nonzero numbers, therefore overflow is not tested

- Underflow is set if an illegal number is detected at the start of the operation in either the BX- or QX-Registers.

### Normalized Floating-Point Mode

- M and M+1 are loaded into the BX-Register. The AX-Register is cleared

- The exponent of QX is transferred to AX<sub>E</sub>

- ullet A check is made to determine if  $BX_m$  or  $QX_m$  contain an illegal number. If either or both do, the operation is terminated and an UNDERFLOW (and illegal number) indication in the AAU

- $\bullet$  If both registers contain legal numbers, the exponents of AX and BX are added and stored in AX\_E. This completes the addition of the exponents operation and the sum of QX\_E and BX\_E and stored in AX\_E

- The BX and QX mantissas are examined for zero content and, if found to contain zeros, the operation is terminated with AX- and QX-Registers cleared

- If the mantissas of BX and QX are nonzero, legal numbers, the mantissas in AX and QX are shifted right together until a 1-bit is detected in position QX-39. Addition or subtraction of  $AX_m$  plus  $BX_m$  forms the first partial product in AX and continues in this fashion until a 60-bit product is formed in  $AX_m$  and  $QX_m$ . The products is normalized and the exponent in QX-Register is set to  $AX_E$ -30. If  $QX_E$  underflows, no error is set. The mantissas signs QX(20) and AX(20) are set to agree

- A check is made to determine if overflow or underflow occurred

- Overflow is set if the product in the AX-Register exceeds +25510

- <u>Underflow</u> is set:

- 1. If an illegal number is detected in the mantissa at the start of the operation in either the QX- or BX-Registers.

- If the exponent product in AX is less than -256<sub>10</sub>. The AX- and QX-Registers are cleared.

<u>Unnormalized Floating-Point Mode.</u> Same condition prevails as set forth for normalized floating-point mode, except:

Product in AX- and QX-Registers is left in unnormalized form.

Figure 12 illustrates the execution of the FMP instruction during a fixed-point mode of operation.

Figure 13 illustrates the execution of the FMP instruction during a floating-point mode of operation.

Figure 12. Fixed-Point FMP

À

Figure 13. Floating-Point FMP

#### DIVIDE

| <del></del>    |              |   |         |  |

|----------------|--------------|---|---------|--|

| $\mathtt{FDV}$ | $\mathbf{M}$ | X | 36MMMMM |  |

|                |              |   |         |  |

The contents of AX and QX are divided algebraically by the contents of M and M+1. The contents of M and M+1 are unchanged.

#### Fixed-Point Mode

- M and M+1 are loaded into the BX-Register

- If the AX-Register is negative (AX-0 determines the sign of the entire number in AX- and QX-Registers), the AX- and QX-Registers are complemented

- A check is made to determine if either the AX-, QX-, or BX-Registers contain illegal numbers. If any of them do, the arithmetic operation is terminated with an UNDER-FLOW (and illegal number) indicator set in the AAU. The original dividend is left in the AX- and QX-Registers (or the 2's complement if the original dividend was negative)

- If the registers contain legal numbers the BX-Register is checked to determine if it contains zeros (this is the divisor). If the divisor in BX is zero, a divide check error condition exists and the OVERFLOW and DIVIDE CHECK indicator will be set. If the subsystem is in the trapping mode the divide check error condition will not set the OVERFLOW indicator, but it will set the DIVIDE CHECK indicator.

- A check is made to determine if the absolute value of that part of the dividend in the AX-Register is equal to or greater than the absolute value of the divisor. If true, the instruction is terminated with a divide check error and the OVERFLOW and DIVIDE CHECK indicators are set. The original dividend is in the AX- and QX-Registers (or the 2's complement if the original was negative)

- A check is made to determine the zero content of the AX- and QX-Registers. If they are zero, the instruction is terminated

- The contents of the AX- and QX-Registers are divided algebraically by the contents of the BX-Register. The quotient is stored in the AX-Register, with the remainder in the QX-Register and the sign bits set to the sign of the original dividend

- The QX-Register is tested for an illegal number. The only way that QX can contain an illegal number is when the remainder is zero and the sign of the original dividend is negative. If it is found to be illegal, the QX-Register is cleared

- The AX-Register is tested for an illegal number. The only way that AX can contain an illegal number is when the quotient is zero and the sign negative. If it is found to be illegal, the AX-Register is cleared

- Overflow is set if a divide check error is detected during a divide operation. The AX- and QX-Registers are not cleared

- <u>Underflow</u> is set if an illegal number is detected in either the AX-, QX-, or BX-Registers.

#### Normalized Floating-Point Mode

- The floating-point number in M and M+1 is loaded into the BX-Register

- If the dividend is negative--AX-20 determines the sign of the dividend--the mantissas of AX and QX are complemented

- The exponent of the remainder is formed by subtracting 30 from the exponent in AX.  $AX_E-30$  to  $QX_E$ . If the exponent underflows, it is left in  $QX_E$  as a positive number (-255 -30 = +29) and underflow is not set

- The mantissas of the AX-, QX-, and BX-Registers are checked for illegal numbers. If there is an illegal number present, the operation is terminated with an UNDER-FLOW (an illegal number) indicator in the AAU

- The exponent of the quotient is formed by algebraically subtracting the divisor exponent from the dividend exponent

- A check is made to determine if the mantissa in the BX-Register contains zeros. If so, the OVERFLOW and DIVIDE CHECK indicators are set in the AAU

- A check is made to determine if the absolute value of the dividend mantissa is equal to or greater than the absolute value of the divisor mantissa. If it is, the mantissas of AX and QX are shifted right one place and the exponents are increased by one

- Another check is made to determine if the absolute value of the dividend mantissa is equal to or greater and if it is the OVERFLOW and DIVIDE CHECK indicators are set in the AAU. If they are not equal to or greater, the mantissas of AX and QX are checked for zero

- If both AX- and QX-Registers contain zero, AX and QX are cleared and the arithmetic operation is terminated

- If the mantissas of AX and QX are nonzero, the contents (mantissas) are divided algebraically by the mantissa of BX. The quotient is stored in AX and the remainder is stored in QX with the sign of the original dividend

- The mantissa in AX is normalized

- The mantissa of QX is tested for illegal number or zero content. If it is found true, the AX-Register is cleared

- Overflow is set:

- 1. If the exponent of the quotient in the AX-Register exceeds  $+255_{10}$ .

- 2. If a divide check error is detected at the start of the operation and the AAU is in the non-trapping mode. Overflow is not set if the AAU is in the trapping mode.

- Underflow is set:

- 1. If an illegal number is detected in the AX-, QX-, or BX-Registers

- 2. If the resultant AX exponent is less than +256, the AX- and QX-Registers are cleared

<u>Unnormalized Floating-Point Mode.</u> Same conditions prevail as set forth for normalized floating-point mode, except:

Quotient in the AX-Register is left in unnormalized form.

Figure 14 illustrates the execution of the FDV instruction during a fixed-point mode of operation.

Figures 15, 16 and 17 illustrate the execution of the FDV instruction during a floating-point mode of operation.

Figure 14. Fixed-Point FDV

Figure 15. Floating-Point FDV

Figure 16. Setting Divide Check

Figure 17. Normalization Floating-Point FDV

<u>DATA TRANSFER INSTRUCTIONS</u> are those which transfer data between the AAU and central processor. The instruction must specify a memory location address greater than 15 unless it is index modified. The instructions for data transfer are FLD and FST. They are not dependent on an operating mode.

#### LOAD AX REGISTER

## FLD M X 30MMMMM

- Contents of M and M+1 replace contents of AX-Register.

- Contents of M (even) are loaded into AX 0-19

- Contents of M+1 (odd) are loaded into AX 20-39

- Contents of M and M+1 are unchanged

- Contents of M (odd) are loaded into AX 0-19 and 20-39.

- Illegal numbers may be loaded. Only when an attempt is made to use the illegal number as an arithmetic operand is the illegal condition set.

#### STORE AX REGISTER

# FST M X 33MMMMM

- Contents of AX-Register replace contents of M and M+1 if M is even

- Contents of AX-Register are not changed

- Contents of AX-Register 0-19 are stored in M if M is odd and then the contents of AX 20-39 are written over 0-19 in the same location M.

#### Test-and-Branch Instructions

All AAU test-and-branch instructions are indicated by BAR in the Operation field followed by a 3-letter mnemonic code in the Operand field of the General Assembly Program coding sheet. Test-and-branch instructions interrogate the AAU for specific conditions which, if true, cause the next sequential instruction to be executed. If false, the second sequential instruction is executed. A 7 must be shown in the X field of the coding sheet.

Each test-and-branch instruction is described below.

#### BRANCH ON AAU READY

#### BRANCH ON AAU NOT READY

| BAR    | BAR       | 7                            | 2514720            | BAR         | BAN    | 7                  | 2516720                              |

|--------|-----------|------------------------------|--------------------|-------------|--------|--------------------|--------------------------------------|

| The AA | AU is tea | sted to determ<br>struction. | ine if it is ready | The<br>read | AAU is | tested<br>pt an in | to determine if it is not struction. |

| BRANCH | ONT | A ATT | BATRITIC |

|--------|-----|-------|----------|

| BRANCH | ON  | AAU   | MIINOS   |

#### BRANCH ON AAU PLUS

| BAR      | BMI                  | 7                                | 2514721                                                       | BAR             | BPL                   | 7                       | 2516721                                                                                    |

|----------|----------------------|----------------------------------|---------------------------------------------------------------|-----------------|-----------------------|-------------------------|--------------------------------------------------------------------------------------------|

| in bit p | osition (            | ), if in the fi<br>gn in bit pos | for a minus sign<br>xed-point mode or<br>sition 20, if in the | bit p<br>floati | osition 2<br>ng-point | 0 (sign of mode of      | ested for a plus sign in f the mantissa) if in the r for a plus sign in bit ed-point mode. |

| BRANC    | H ON AA              | U ZERO                           |                                                               | BRA             | NCH ON                | AAU NOT                 | ZERO                                                                                       |

| BAR      | BZE                  | 7                                | 2514722                                                       | BAR             | BNZ                   | 7                       | 2516722                                                                                    |

| The AX   | -Registe             | r is tested for                  | total zero content.                                           | The             | AX-Regi               | ster is te              | ested for nonzero content.                                                                 |

| BRANC    | H ON OV              | ERFLOW                           |                                                               | BRA             | NCH ON                | no over                 | FLOW                                                                                       |

| BAR      | BOV.                 | 7                                | 2514723                                                       | BAR             | BNO                   | . 7                     | 2516723                                                                                    |

|          |                      | W indicator :<br>icator not res  |                                                               | The<br>off co   | OVERF1                | LOW indi<br>(indicator  | cator is tested for the not reset).                                                        |

| NOTE:    | These a              | re not tests fo                  | or the OVERFLOW                                               | HOLI            | ) indicate            | or,                     |                                                                                            |

| BRANC    | H ON UN              | DERFLOW                          |                                                               | BRA             | NCH ON                | NO UNDE                 | RFLOW                                                                                      |

| BAR      | BUF                  | 7                                | 2514724                                                       | BAR             | BNU                   | 7                       | 2516724                                                                                    |

|          |                      | OW indicator<br>licator is not   | is tested for an reset).                                      |                 |                       |                         | licator is tested for an is not reset).                                                    |

| NOTE:    | These a              | re not tests fo                  | or the UNDERFLO                                               | w hoi           | D indica              | tor.                    |                                                                                            |

| BRANC    | H ON OV              | ERFLOW HO                        | LD ON                                                         | BRA             | NCH ON                | OVERFLO                 | OW HOLD OFF                                                                                |

| BAR      | воо                  | 7                                | 2514725                                                       | BAR             | BON                   | 7                       | 2516725                                                                                    |

| The AA   | AU is tes<br>the ind | ted for the C<br>licator is on   | OVERFLOW HOLD, it is turned off.                              | The off.        | AAU is<br>If the      | tested for<br>indicator | the OVERFLOW HOLD is on, it is turned off.                                                 |

| BRANC    | H ON UN              | DERFLOW H                        | OLD ON                                                        | BRA             | NCH ON                | UNDERF                  | LOW HOLD OFF                                                                               |

| BAR      | BUO                  | 7                                | 2514726                                                       | BAR             | BUN                   | 7                       | 2516726                                                                                    |

|          |                      |                                  | DERFLOW HOLD<br>n, it is turned off.                          |                 |                       |                         | the UNDERFLOW HOLD is on, it is turned off.                                                |

#### BRANCH ON ERROR

#### BRANCH ON NO ERROR

| BAR     | BER        | 7       | 2514727                | BAR    | BNE       | 7.           | 2516727                  |

|---------|------------|---------|------------------------|--------|-----------|--------------|--------------------------|

| The A   | AU is te:  | sted fo | r either the OVERFLOW, | The A  | AAU is te | sted for DIV | or either the OVERFLOW,  |

| UNDER   | RFLOW,     | or DI   | VIDE CHECK indicators  | UNDE   | CRFLOW,   |              | IDE CHECK indicators off |

| on (ind | licators a | re not  | reset).                | (indic | ators are |              | set).                    |

NOTE: These are not tests for the OVERFLOW HOLD or UNDERFLOW HOLD indicators. The divide check tested by this command is an internal "instruction divide check." The program accessible DIVIDE CHECK is a "hold" type indicator, whereas the internal divide check is not.

#### BRANCH ON DIVIDE CHECK ON

#### BRANCH ON DIVIDE CHECK OFF

| BAR                      | BDC       | 7             | 2514730                                               | BAR                   | BDN       | .7              | 2516730                                               |

|--------------------------|-----------|---------------|-------------------------------------------------------|-----------------------|-----------|-----------------|-------------------------------------------------------|

| The I<br>an on<br>turned | condition | HECK<br>a. If | indicator is tested for<br>the indicator is on, it is | The<br>an of<br>turne | f conditi | CHECK<br>on. If | indicator is tested for<br>the indicator is on, it is |

| BRANG                    | TH ON II. | Ι.ΕΔΑΙ        | NIIMBER                                               | BRAN                  | ICH ON N  | O II I E        | CAI MIMPED                                            |

| BAR    | BIL                   | 7         | 2514731             | BAR   | BNI       | 7                   | 2516731             |

|--------|-----------------------|-----------|---------------------|-------|-----------|---------------------|---------------------|

| The AA | AU illeg<br>on condit | al number | condition is tested | The A | AAU illeg | gal number<br>tion. | condition is tested |

NOTE: If the illegal number is on, it is turned off by either of these instructions.

#### BRANCH ON FIXED-POINT MODE ON

#### BRANCH ON FIXED-POINT MODE OFF

| BAR   | BFX | 7       |          | 2514   | 732 | BAR | BN                | x | 7   |           |    | 251673    | 2  |    |

|-------|-----|---------|----------|--------|-----|-----|-------------------|---|-----|-----------|----|-----------|----|----|

| The F |     | NT indi | cator is | tested | for |     | FIXED<br>ondition |   | INT | indicator | is | tested fo | or | an |

NOTE: If the indicator is on, it is not reset by either of these instructions.

#### BRANCH ON UNNORMALIZED FLOATING-POINT ON

#### BRANCH ON UNNORMALIZED FLOATING-POINT OFF

| BAR | в    | ĮΡ             | 7                   | 2       | 514733            | BAR        | BNP                       | 7      | 25      | 16733     |

|-----|------|----------------|---------------------|---------|-------------------|------------|---------------------------|--------|---------|-----------|

| The | FLOA | TING<br>r an o | -POINT<br>n conditi | UN-NORM | indicato <b>r</b> | The is tes | FLOATING<br>sted for an o | -POINT | UN-NORM | indicator |

NOTE: If the indicator is on, it is not reset by either of these instructions.

### BRANCH ON NORMALIZED FLOATING FLOATING-POINT ON

### BRANCH ON NORMALIZED FLOATING-POINT OFF

| BAR | BNF                  | 7 | 2514734   |    | BAR | BNN                      | 7 | 2516734             |

|-----|----------------------|---|-----------|----|-----|--------------------------|---|---------------------|

|     | LOATING<br>for an on |   | indicator | is |     | FLOATING<br>d for an off |   | NORMAL indicator is |

NOTE: If the indicator is on, it is not reset by either of these instructions.

#### PROGRAM CONSIDERATIONS

Unlike the requirements for peripherals with controllers having access to the central processor through its priority control, the AAU is always connected to the central processor and only a SET instruction is required to select the mode of operation.

#### Setting the Calculation Mode

Once a SET MODE instruction is given, it need not be given again until the programmer wants to change modes. The instructions required to perform the desired arithmetic operations follow the mode setting instructions. To illustrate, Figure 18 shows a program which begins calculations in the normalized floating-point non-trapping mode and then switches to the unnormalized floating-point non-trapping mode as directed by the new SET instruction shown on line 12.

#### General Assembly Program Coding:

| L        |   |    | Syn | odı | 1        |   |   |   | 0         | pr           |           |          |    |          | Оре                                    | rand                                   | ł                                            |                                              |              | X        | REMARKS                              |

|----------|---|----|-----|-----|----------|---|---|---|-----------|--------------|-----------|----------|----|----------|----------------------------------------|----------------------------------------|----------------------------------------------|----------------------------------------------|--------------|----------|--------------------------------------|

|          | 1 | 2  | 3   | 4   | Γ        | 8 | 6 | 8 | ĺ         | 9            | 10        | 12       | 13 | 14       | 1 5                                    | 16                                     | 17                                           | 18                                           | 19           | 20       | 31                                   |

| L        |   | S, | Т   | A   | , F      | 3 | Т | s | , .       | E,           | Т         | N        | F  | L        | , P                                    | O                                      | I                                            | N                                            | , <b>T</b>   |          | Set normalized floating-point mode   |

|          |   |    |     | 1   |          |   |   | F | ٠, :      | L,           | D         | D        | R  |          |                                        |                                        |                                              |                                              |              |          | Κ.:                                  |

|          |   |    |     | :   | ,        |   |   |   |           |              | U.        |          | R  |          | ,                                      |                                        |                                              |                                              |              |          | ·                                    |

| $\Gamma$ |   |    |     |     |          |   |   |   |           |              | Т         |          |    | M        | . 1                                    |                                        |                                              | <del></del>                                  |              |          |                                      |

|          |   |    |     |     |          |   |   | 1 |           | <u> </u>     | 1         | Ī        | L  | <u>,</u> |                                        |                                        |                                              |                                              |              |          |                                      |

|          |   |    |     |     |          |   |   | 7 | -         | )            | 1         |          |    | <u> </u> | <del></del>                            |                                        | •                                            | -                                            |              |          |                                      |

|          |   |    |     |     |          |   |   | 1 | 7         | Γ            | $\dagger$ | <u> </u> |    |          | ــــــــــــــــــــــــــــــــــــــ |                                        |                                              | .1                                           | +            |          |                                      |

| T        | , |    |     |     | -        |   |   | 1 | "(        |              | t         |          | ·  | 1        |                                        |                                        |                                              | 1                                            | +            |          |                                      |

|          |   | _  |     | _   |          |   |   | ) | +(        | ├ <u>-</u> - | $\dagger$ |          | L  |          | -                                      | ــــــــــــــــــــــــــــــــــــــ | -                                            | +                                            |              |          | ·                                    |

|          |   |    |     |     | +        |   |   | 1 |           |              | 1         |          | i  |          |                                        | +                                      | +                                            |                                              | +            |          |                                      |

| $\vdash$ |   |    | _   |     |          |   |   | _ | لد        |              | _         | _        | _  |          | <del>-</del>                           | <del></del>                            |                                              | +                                            | -            |          |                                      |

| -        |   | _  |     |     | _        |   |   |   |           |              |           |          |    |          |                                        | 0,                                     |                                              | +                                            | +            |          |                                      |

| $\perp$  |   |    |     |     | ٠        | 1 |   | S | <u> 1</u> | Ξ,           | T         | U        | F  | L        | P                                      | 0                                      | Ι                                            | N                                            | $\mathbf{T}$ |          | Set unnormalized floating-point mode |

|          |   |    |     |     |          | , |   | F | . I       | .,           | D         | G        | Α  |          |                                        |                                        |                                              |                                              |              | ·        |                                      |

|          |   |    |     |     |          |   |   | , | 7         | 4            |           |          |    |          |                                        |                                        |                                              | <u> </u>                                     |              |          |                                      |

|          |   |    |     |     | <u> </u> |   |   |   | -         | Γ,           |           |          |    |          |                                        | 1                                      | 1                                            | <u> </u>                                     | ╙┤           | $\dashv$ |                                      |

| -        | - |    |     |     |          |   |   |   | 1/        | 4            |           |          |    |          |                                        | _                                      | <u>.                                    </u> | <u>.                                    </u> |              |          |                                      |

Figure 18. Setting Mode For Calculation

#### Setting the Trapping Mode

The trapping mode, a standard feature of the GE-235 AAU, operates in a manner similar to the Automatic Program Interrupt (API). Automatic Program Interrupt is explained in the GE-235 Central Processor Reference Manual (CPB-374).

API is not affected by the trapping mode. If a peripheral device terminates on exactly the same memory cycle in which a trap occurs, the program interrupt (API) will be taken first. The AAU trap signal is not dropped until the trap is executed, but the trap is not executed if the central processor is executing the priority program. The first instruction in sequence—after program control is returned to the main program (from API mode)—will not be executed, the AAU trap will be executed.

If a peripheral device should become ready while the central processor is executing the trap routine, control is transferred to the API routine and executed. Upon completion of the API routine, control is transferred back to the trap routine.

An API routine should not use the trap mode. If it does, the trap interrupt does not take place. It is remembered however, and the trap interrupt is executed <u>after</u> control is returned to the central processor from the API routine.

When the trapping mode is entered by a SET TRPMODE instruction, operation is as follows:

- The OVERFLOW HOLD, UNDERFLOW HOLD and DIVIDE CHECK indicators (an illegal number sets the UNDERFLOW indicator) are neither reset nor disabled